주요 연구성과

NEW 서형탁 교수팀, 미래 반도체 핵심 기술 활용 가능 신소자 개발

- 2023-06-30

- 2235

아주대 연구진이 차세대 지능형 반도체에 활용 가능한 신소자를 개발했다. 기존의 플래시 메모리보다 빠르게 적은 에너지로 다양한 연산을 구현할 수 있어 인공지능 컴퓨팅과 빅데이터 처리 등에 폭넓게 활용될 전망이다.

서형탁 교수(첨단신소재공학과·대학원 에너지시스템학과) 연구팀은 강유전성 초박막 소재의 나노 위상 분극 도메인 정보 저장 및 스위칭 제어 기술을 이용하여 연산과 비메모리 기능이 통합된 프로세스-인-메모리(PIM) 터널링 소자 개발에 성공했다고 밝혔다.

연구 내용은 "초고속 로직-인-메모리 동작 구현을 위한 헤프늄-지르코니아 나노라미네이트 기반 의 스위칭 가능한 극성 나노텍스츄어(Switchable Polar Nanotexture in Nanolaminates HfO2-ZrO2 for Ultrafst Logic-in-Memory Operations)"라는 제목으로 나노융합기술 분야 저명 국제 학술지인 <스몰(Small)> 3월호 온라인판에 게재됐다. 이번 연구에는 아주대 대학원 에너지시스템학과 쿠마 모히트(Mohit Kumar) 교수가 제1저자로, 아주대 대학원 한승익·안영환·전예린·박지영 학생이 공저자로 참여했다. 서형탁 교수는 교신저자로 함께 했다.

PIM(Process-in-Memory)은 뇌의 신경회로를 모사해 메모리와 프로세서를 통합한 신개념 반도체로 미래 반도체 핵심 기술이다. 현재 반도체 집적회로는 메모리와 프로세서가 분리되어 데이터를 처리하는 '폰노이만 아키텍쳐(Von Neumann architecture)' 방식을 이용한다. 그러나 최근 인공지능(AI) 컴퓨팅과 빅데이터 처리 등을 위해 메모리와 프로세서 간 데이터 전달량이 증가함에 따라 처리 속도가 한계에 이르는 '폰노이만 병목현상'이 발생하고 있다. 이에 메모리와 프로세서를 통합해 빠른 연산 처리 속도를 구현하고, 전력 소모량도 아낄 수 있는 PIM 기술이 주목받고 있다.

이러한 PIM 소자를 구현하기 위해 전 세계 반도체 제조사들은 기존 실리콘 집적회로 소재와 공정을 기반으로 회로 구조적인 변화를 시도함과 동시에 실리콘 소재에서 탈피하여 멤리지스터(메모리+레지스터)와 멤트랜지스터(메모리+트랜지스터)와 같은 신소자를 이용한 개발을 진행하고 있다. 그러나 PIM 기술이 목표로 하는 저전력·고속 스위칭·멀티 레벨 스위칭의 신뢰성을 모두 확보한 신기술의 개발은 아직 요원하다. 특히 나노 스케일의 단위 소자에서 안정적인 비휘발성 저장 및 논리 연산을 저전력·초고속으로 달성한 결과는 아직 보고되지 않았다.

아주대 연구팀은 PIM 신소자 개발을 위해 헤프늄-지르코늄 복합산화물(HfZrO: HZO)에 주목했다. HZO는 차세대 저전력 트랜지스터의 후보군인 음의 정전저항기반 트랜지스터에 사용되는 핵심 소재로, 외부 전기장에 따라 비휘발성 분극이 강하게 일어나는 강유전성을 가지며 특히 3차원 구조의 집적회로 핵심 공정인 원자층 증착이 가능하여 반도체 분야에서 널리 연구 개발되고 있는 소재다.

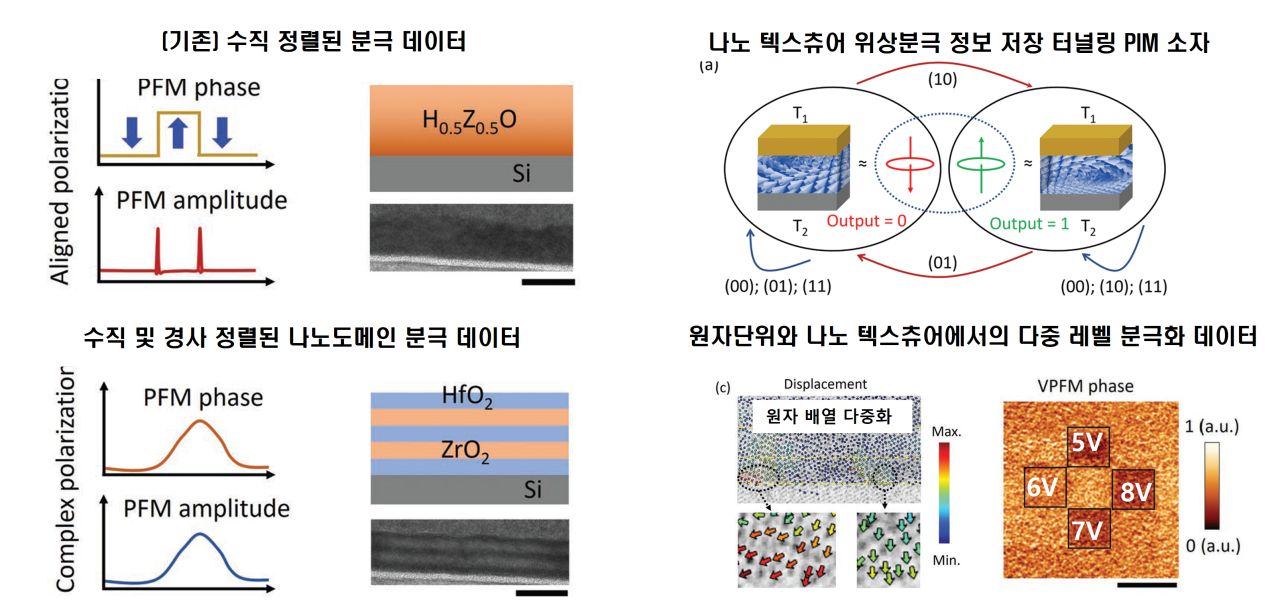

HZO의 강유전성은 이상적으로는 전압의 부호에 따라 상향 및 하향 수직 정렬 분극화가 소재 전체에 일관되게 일어나는 것이 필요하지만, 원자층 증착된 HZO는 나노결정구조를 가지기 때문에 각 결정립의 분포에 따라 수직 정렬 분극뿐만 아니라 경사 정렬 분극화가 점진적으로 발생하는 '위상 극성 도메인'이 형성된다. 연구팀은 이러한 위상 극성 도메인을 제어할 수 있다면, 각 나노스케일의 도메인에 정보를 비휘발성으로 저장하고 다양한 논리 연산을 구현할 수 있음에 착안하여 개발을 진행했다.

아주대 연구팀은 실리콘(Si) 기판 위에 헤프늄 산화물과 지르코니움 산화물을 나노레미네이트 방식의 플라즈마 원자층 증착 공정으로 순차적으로 번갈아 가며 증착하되, 완전히 균일한 박막 1종과 각 단일 층이 교차된 상태를 유지하는 박막 1종을 확보하는 공정을 개발했다. 그리고 원자현미경을 이용한 나노 스케일 분극 스위칭과 분석을 통해 교차 구조를 유지하는 박막의 경우에는, 분극화가 수직 정렬뿐 아니라 경사 정렬될 수 있고 이를 통하여 정보를 멀티레벨로 저장할 수 있음을 최초로 확인했다.

이번에 개발한 소자를 이용하면 80나노 초(nsec)에서 쓰기 및 읽기 동작이 가능하고, 온·오프(on·off) 비율, 스위칭 반복성(Endurance), 비휘발성(데이터 저장 시간) 기능이 모두 기존의 소자 대비 우수하다. 더불어 아주대 연구팀은 하나의 단위 소자에서 비휘발성 스위칭 조합을 이용, NAND, NOR, OR, AND 등 총 14가지 논리 연산 기능을 다치레벨로 구현하여 비휘발성 PIM의 필수 특성을 모두 확인했다.

서형탁 교수는 "AI 컴퓨팅과 빅데이터 처리 등을 위해 차세대 지능형 반도체를 개발하고자 하는 노력이 이어지고 있다"며 "완전히 새로운 구조와 공정, 소자 등 다방면의 연구가 진행 중인 가운데, 이번 연구는 현재 양산 공정이 확보된 강유전성 소재를 기반으로 나노 도메인 분극화를 이용하여 정보를 비휘발성·다중레벨로 구현한 최초의 사례"라고 설명했다.

서 교수는 이어 "실리콘 접합 구조의 터널링 소자 구조를 구현하여 양산 공정 적용이 가능하다"며 "인공지능형 컴퓨팅에 적합한 회로 개발을 위해 다른 분야 연구자들과 협업하여 상용화를 목표로 후속 연구를 진행할 예정"이라고 덧붙였다.

한편 이번 연구는 과학기술정보통신부·한국연구재단이 주관하는 PIM인공지능반도체 핵심기술개발 사업과 기본·중견 기초연구지원사업의 지원으로 수행되었으며, 특허 출원이 진행 중이다.

(왼쪽)기존 강유전성 HZO의 경우 상하 수직 분극 정렬만 존재하나 나노라미네이트 구조의 경우 경사 분극 정렬이 혼재되어 다중 분극 상태 제어가 가능함 (오른쪽 아래)투과전자현미경 분석을 통해 원자레벨에서 다중 원자 정렬이 존재함을 입증하였고 전압 크기에 따라 다치레벨의 분극화를 전압 크기에 따라 제어가능함을 원자현미경 분석을 통해 입증 (오른쪽 위)최종 나노텍스츄어의 다중 분극화를 이용한 양자역학적 터널링 메모리-로직연산 통합 소자의 개략도

* 위 사진 설명 - 뒷줄 왼쪽부터 시계방향으로 한승익 학생, 서형탁 교수, 쿠마 모히트(Mohit Kumar) 교수, 박지영 학생, 전예린 학생